TSMC (TWSE: 2330, NYSE: TSM) hat heute auf dem 2024 North

America Technology Symposium des Unternehmens seine neuesten

Halbleiterprozesse, fortschrittlichen Packaging- und

3D-IC-Technologien vorgestellt, die die nächste Generation von

KI-Innovationen mit Silizium-Führerschaft antreiben werden. TSMC

hat die TSMC A16™ Technologie mit führenden Nanoblech-Transistoren

mit innovativer Rückseiten-Stromschienenl�sung für die Produktion

im Jahr 2026 vorgestellt, die eine deutlich verbesserte Logikdichte

und Leistung bringt. TSMC stellte auch seine System-on-Wafer

(TSMC-SoW™) Technologie vor, eine innovative L�sung, die

revolutionäre Leistung auf Waferebene bringt, um die zukünftigen

KI-Anforderungen für Hyperscaler-Rechenzentren zu erfüllen.

In diesem Jahr jährt sich das North America Technology Symposium

von TSMC zum 30. Mal. Mehr als 2.000 Teilnehmer besuchten die

Veranstaltung, die vor 30 Jahren noch weniger als 100 Teilnehmer

zählte. Das North America Technology Symposium in Santa Clara,

Kalifornien, bildet den Auftakt zu den TSMC Technology Symposien,

die in den kommenden Monaten weltweit stattfinden werden. Das

Symposium bietet auch eine „Innovationszone“, in der die

technologischen Errungenschaften unserer aufstrebenden

Start-up-Kunden vorgestellt werden.

„Wir treten in eine KI-gestützte Welt ein, in der künstliche

Intelligenz nicht nur in Rechenzentren, sondern auch in PCs,

mobilen Geräten, Automobilen und sogar im Internet der Dinge zum

Einsatz kommt“, sagte TSMC-CEO Dr. C.C. Wei. „Wir bei TSMC bieten

unseren Kunden die umfassendste Palette an Technologien, um ihre

Visionen für KI zu verwirklichen – vom weltweit fortschrittlichsten

Silizium über das breiteste Portfolio an fortschrittlichen

Packaging- und 3D-IC-Plattformen bis hin zu Spezialtechnologien,

die die digitale Welt mit der realen Welt verbinden.“

Zu den neuen Technologien, die auf dem Symposium vorgestellt

wurden, geh�ren:

TSMC A16™ Technologie: Nachdem TSMCs branchenführende

N3E-Technologie nun in Produktion ist und N2 in der zweiten Hälfte

des Jahres 2025 in Produktion gehen soll, stellte TSMC mit A16 die

nächste Technologie auf seiner Roadmap vor. A16 wird die Super

Power Rail-Architektur von TSMC mit den Nanoblech-Transistoren von

TSMC kombinieren und soll ab 2026 produziert werden. Sie verbessert

die Logikdichte und die Leistung, indem sie den Signalen

Routing-Ressourcen auf der Vorderseite widmet. Damit ist die A16

ideal für HPC-Produkte mit komplexen Signalwegen und dichten

Stromversorgungsnetzwerken. Im Vergleich zum N2P-Prozess von TSMC

bietet A16 eine 8-10%ige Geschwindigkeitsverbesserung bei gleicher

Vdd (positive Versorgungsspannung), eine 15-20%ige

Leistungsreduzierung bei gleicher Geschwindigkeit und eine bis zu

1,10-fache Verbesserung der Chipdichte für

Rechenzentrumsprodukte.

TSMC NanoFlex™ Innovation für Nanoblech-Transistoren: Die

kommende N2-Technologie von TSMC wird mit TSMC NanoFlex geliefert,

dem nächsten Durchbruch des Unternehmens bei der gemeinsamen

Optimierung von Design und Technologie. TSMC NanoFlex bietet

Designern Flexibilität bei N2-Standardzellen, den Grundbausteinen

des Chipdesigns, wobei kurze Zellen den Schwerpunkt auf eine kleine

Fläche und eine h�here Energieeffizienz legen und hohe Zellen die

Leistung maximieren. Kunden sind in der Lage, die Kombination von

kurzen und langen Zellen innerhalb desselben Designblocks zu

optimieren und ihre Designs so abzustimmen, dass sie den optimalen

Kompromiss zwischen Stromverbrauch, Leistung und Fläche für ihre

Anwendung erreichen.

N4C Technologie: TSMC hat N4C angekündigt, eine

Erweiterung der N4P-Technologie mit bis zu 8,5 % niedrigeren Kosten

für integrierte Schaltkreise und geringem Adoptionsaufwand, die ab

2025 in Serie produziert werden soll, um die fortschrittliche

Technologie von TSMC für ein breiteres Spektrum von Anwendungen

einzusetzen. N4C bietet flächeneffiziente Basis-IP und

Design-Regeln, die vollständig mit dem weit verbreiteten N4P

kompatibel sind und eine bessere Ausbeute durch die Verringerung

der Gr�ße der integrierten Schaltkreise erm�glichen. Damit bietet

N4C eine kosteneffektive Option für Value-Tier-Produkte, die auf

den nächsten fortschrittlichen Technologieknoten von TSMC

migrieren.

CoWoS®, SoIC und System-on-Wafer (TSMC-SoW™):

Der Chip on Wafer on Substrate (CoWoS®) von TSMC hat die

KI-Revolution entscheidend vorangetrieben, da er es den Kunden

erm�glicht, mehr Prozessorkerne und HBM-Stacks (High-Bandwidth

Memory) nebeneinander auf einem Interposer unterzubringen.

Gleichzeitig hat sich unser System on Integrated Chips (SoIC) als

führende L�sung für das 3D-Chipstacking etabliert, und Kunden

kombinieren CoWoS zunehmend mit SoIC und anderen Komponenten für

die ultimative System-in-Package (SiP) Integration.

Mit System-on-Wafer bietet TSMC eine revolutionäre neue

M�glichkeit, eine große Anzahl von integrierten Schaltkreisen auf

einem 300-mm-Wafer unterzubringen, die mehr Rechenleistung bietet

und dabei weit weniger Platz im Rechenzentrum ben�tigt und die

Leistung pro Watt um Gr�ßenordnungen erh�ht. Das erste SoW-Angebot

von TSMC, ein reiner Logik-Wafer auf Basis der Integrated Fan-Out

(InFO)-Technologie, befindet sich bereits in der Produktion. Eine

Chip-on-Wafer-Version, die die CoWoS-Technologie nutzt, soll 2027

fertiggestellt sein und die Integration von SoIC, HBM und anderen

Komponenten erm�glichen, um ein leistungsfähiges System auf

Waferebene zu schaffen, dessen Rechenleistung mit der eines

Server-Racks im Rechenzentrum oder sogar eines ganzen Servers

vergleichbar ist.

Silicon Photonics Integration: TSMC entwickelt die

Compact Universal Photonic Engine (COUPE™)-Technologie, um das mit

dem KI-Boom einhergehende explosionsartige Wachstum bei der

Datenübertragung zu unterstützen. COUPE nutzt die SoIC-X

Chip-Stacking-Technologie, um einen elektrischen integrierten

Schaltkreis auf einen photonischen Schaltkreis zu stapeln. Dies

bietet die niedrigste Impedanz an der

Schaltkreis-zu-Schaltkreis-Schnittstelle und eine h�here

Energieeffizienz als herk�mmliche Stacking-Methoden. TSMC plant,

COUPE im Jahr 2025 für kleine Formfaktor-Pluggables zu

qualifizieren, gefolgt von der Integration in CoWoS-Gehäuse als

Co-Packaged Optics (CPO) im Jahr 2026, wodurch optische

Verbindungen direkt in das Gehäuse integriert werden.

Automotive Advanced Packaging: Nach der Einführung des

N3AE "Auto Early"-Prozesses im Jahr 2023 wird TSMC durch die

Integration von fortschrittlichem Silizium und fortschrittlichem

Packaging weiterhin den Bedarf unserer Kunden aus der

Automobilbranche an h�herer Rechenleistung erfüllen, die den

Sicherheits- und Qualitätsanforderungen auf der Straße entspricht.

TSMC entwickelt InFO-oS- und CoWoS-R-L�sungen für Anwendungen wie

fortschrittliche Fahrerassistenzsysteme (ADAS), Fahrzeugsteuerung

und Fahrzeugzentralcomputer und strebt eine Qualifizierung nach

AEC-Q100 Grade 2 bis zum vierten Quartal 2025 an.

Über TSMC

TSMC war ein Pionier des Pure-Play-Foundry-Geschäftsmodells, das

1987 ins Leben gerufen wurde, und ist seither die weltweit führende

Halbleiter-Foundry. Mit branchenführenden Prozesstechnologien und

einem Portfolio an Design-Enablement-L�sungen unterstützt das

Unternehmen ein florierendes Ökosystem von globalen Kunden und

Partnern, um das Innovationspotenzial in der globalen

Halbleiterindustrie freizusetzen. TSMC ist ein auf der ganzen Welt

engagiertes Unternehmen mit Betrieben in Asien, Europa und

Nordamerika.

TSMC setzt 288 verschiedene Prozesstechnologien ein und fertigt

11.895 Produkte für 528 Kunden im Jahr 2023, indem es die breiteste

Palette an fortschrittlichen, speziellen und hochentwickelten

Packagingtechnologien anbietet. Der Hauptsitz des Unternehmens

befindet sich in Hsinchu, Taiwan. Für weitere Informationen

besuchen Sie bitte https://www.tsmc.com.

Die Ausgangssprache, in der der Originaltext ver�ffentlicht

wird, ist die offizielle und autorisierte Version. Übersetzungen

werden zur besseren Verständigung mitgeliefert. Nur die

Sprachversion, die im Original ver�ffentlicht wurde, ist

rechtsgültig. Gleichen Sie deshalb Übersetzungen mit der originalen

Sprachversion der Ver�ffentlichung ab.

Originalversion auf businesswire.com

ansehen: https://www.businesswire.com/news/home/20240424190528/de/

TSMC Pressesprecher:

Wendell Huang

Senior Vice President und CFO

Tel: 886-3-505-5901

Medienkontakte:

Nina Kao

Head of Public Relations

Tel: 886-3-563-6688 DW 7125036

Mobil: 886-988-239-163

E-Mail: nina_kao@tsmc.com

Michael Kramer

Public Relations

Tel: 886-3-563-6688 DW 7125031

Mobil: 886-988-931-352

E-Mail: pdkramer@tsmc.com

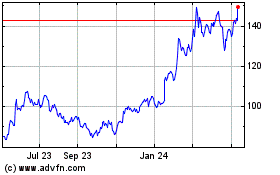

Taiwan Semiconductor Man... (NYSE:TSM)

Historical Stock Chart

From Mar 2024 to Apr 2024

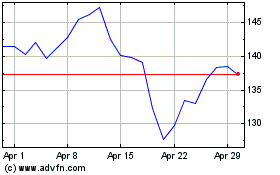

Taiwan Semiconductor Man... (NYSE:TSM)

Historical Stock Chart

From Apr 2023 to Apr 2024